As new devices emerge supporting the new Software-Defined Networking standards, what debug challenges await design engineers?

Software-defined networking (SDN) allows for management of telecom network services by decoupling decisions about where traffic is sent (control plane) from the systems that forward that traffic to its selected destination (data plane). As a new paradigm, it is enjoying tremendous visibility due to its promise to simplify networking and dramatically reduce associated equipment cost. The premise is that off-the-shelf x86 or ARM processors can communicate with high-performance packet forwarding silicon via standard interfaces, thus ending the reign of proprietary ASIC-based solutions.

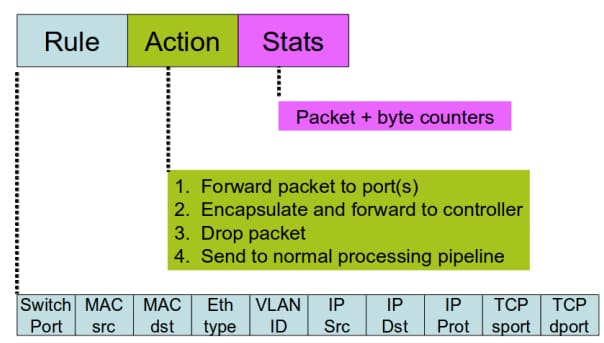

There are numerous specifications associated with this movement towards “open” hardware and software, some of which I covered in a previous blog, High Availability within Software-Defined Networks. OpenFlow is one of the foundational SDN specifications, and provides a method for the control plane to communicate with the data plane. Microsoft recently championed the Switch Abstraction Interface (SAI) through the Open Compute Project (OCP), proposing a standard way to communicate with network switch ASICs. One example of flow-table entries that can be manipulated in an OpenFlow-compliant switch chip is as below:

And new devices are emerging that support these specifications, as suppliers seek to gain a foothold in next-generation, open networking gear. A good example is the Cavium ThunderX family, which is OpenFlow-compliant. ThunderX is differentiated by supporting up to 48 ARMv8 64-bit cores coupled with multiple 10/40/100 GE, SATAv3, and PCI Express ports. ThunderX can be programmed under UEFI, Ubuntu, Fedora, Red Hat, and OpenSUSE, to name a few.

Of course, the debug of such new silicon, along with the complexities of the new SDN API libraries associated with them, makes for tremendous challenges during early board bring-up time. It requires extremely powerful tools to debug and trace a 48-core platform running OpenFlow control plane on fully virtualized core and I/O with hardware acceleration. A good white paper on these challenges and tools is Trace Accelerates Debug Analysis in Complex Linux Systems.