The required Bit Error Rate (BER) of Intel® QuickPath Interconnect (QPI) is 1 error in 10E14 bits. The BER threshold of PCI Express is 1 error in 10E12 bits. What might account for the two orders of magnitude difference?

Some of the underlying technology for Intel® QPI is found in the texts Weaving High Performance Multiprocessor Fabric and Mastering High Performance Multiprocessor Signaling, from Intel press, and both available on Amazon. The books are dated (published 2009 and 2010, respectively), but contain very interesting and useful nuggets on this fascinating bus.

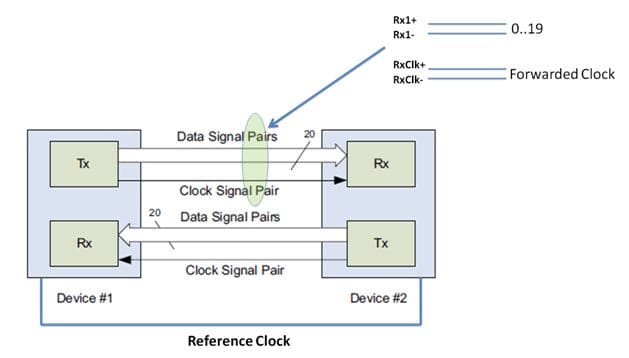

The topology of QPI looks like this:

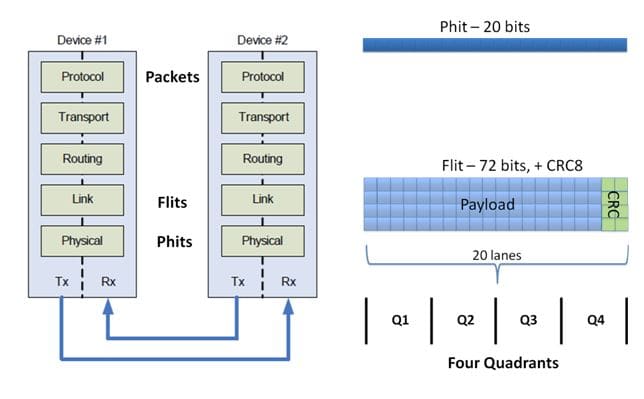

Further, it’s worthwhile to depict the QPI protocol stack, as well as physical layer “phits” and link layer “flits”:

Looking at the above diagrams, and understanding some of the basics of high-speed differential I/O, it is possible to construct a table which compares and contrasts some of the essential features of QPI and PCIe Gen3:

|

Bus |

QPI |

PCIe Gen3 |

|

Speed |

9.6 GT/s |

8.0 GT/s |

|

Encoding |

None |

128b/130b |

|

Scrambling |

Yes |

Yes |

|

Data payload |

72 bits (fixed) |

4096 bytes max (variable) |

|

AC-coupled |

No |

Yes |

|

Embedded clocking |

No |

Yes |

|

CRC |

8 bits (+ 16-bit rolling CRC) |

LCRC of 32 bits (+ 32-bit ECRC) |

We’ll examine some of the underlying implications in an upcoming blog. In the meantime, there’s another interesting blog on QPI and some empirical studies of defects on differential high-speed I/O here.